中科芯集成电路有限公司南京分公司 江苏南京 210000

摘要:随着系统串行信号速率25Gbps或未来更高速率信号的发展,高数串行信号链路上一个很小的阻抗不连续的点都会带来反射,进而影响整个链路的回损、插损、抖动和误码。所以通过什么方法能使这些阻抗不连续的点变得阻抗连续就是目前系统高速串行信号迫切要解决的问题。

关键字:高速串行信号 上升边缩短 阻抗不连续 优化分析

信号完整性的两个重要推论:第一个重要推论,随着上升边的减小(即信号速率越来越高),前述所有信号完整性问题都是以电流或电压的变化速度来衡量的,通常指的是di/dt或dv/dt,上升边越短意味着di/dt或dv/dt越大。随着上升边缩短,噪声问题必然增加,并且难以解决。而且,所有的电子产品中的上升边将持续缩短,这是电子产业的一般趋势。当前没有问题的同一个设计,在下一代设计中就可能出现致命问题。第二个重要推论是,解决信号完整性的有效办法在很大程度上基于对互连线阻抗的理解。如果对阻抗有清晰地直觉认识,而且能够把互连线的物理设计与互连线阻抗联系起来,在设计过程中就能消除许多信号完整性问题。

1.常见的信号链路中会造成阻抗不连续点的几个方面

高速串行信号阻抗不连续点如下:

1)过孔方面

串行信号在实际走线中往往考虑到微带线的串扰和辐射问题,还有信号线连接点空间局限并不能使用微带线进行点到点信号直接连接,往往会打孔将线穿到内层去,带状线连接,信号质量会更好,阻抗也更好控制。但打孔换层同样会带来阻抗不连续点,需要科学的方法去优化阻抗。

2)AC耦合电容方面

串行信号差分通道上通常都有AC耦合电容:1.电容的位置和容值大小都是由芯片公司提供,有些信号比如PCIE要求AC耦合电容靠近通道的发送端,SATA信号要求靠近连接器端,而对于10GBASE-KR信号则要求靠近通道的接收端。2.AC耦合电容本身,包括其扇出引线及对应的电容过孔都是一个阻抗不连续点。

3)背钻方面

在电路板很厚的情况下,如果过孔把串行差分连接到测试焊盘,或者过孔把串行信号连接到相邻层上但又穿越所有板层,则筒状孔壁与板中不同平面层之间通常会有额外的电容量。残余的过孔桩线使过孔就像信号的一个集总容性负载。过孔桩线的电容量与筒状孔壁的尺寸、出砂孔及顶层和底层上焊盘的尺寸、桩线的长度等有密切的关系,其范围从0.1pF到1pF左右。任何与信号线相连的过孔都可以看成容性突变。在高速串接中,它是互连线信号质量的一个主要制约因素,也是一个阻抗不连续点。

2.问题解决方案

针对高速串行链路阻抗不连续造成信号传输质量差的困难,可以从以下几个方面来解决:

1)条件允许的情况下,选择小孔径过孔,对过孔间距优化,过孔反焊盘优化,如图1所示:

图1

过孔优化分为:差分过孔与过孔间距优化、过孔反焊盘优化

首先我们先讲讲过孔与过孔间距优化。已知差分线阻抗为Diff100欧姆,差分过孔处,由于出现了大的过孔焊盘,所以总的差分阻抗在过孔处是会被拉低于100欧姆的,那么我们怎么样把过孔拉低的阻抗给拉回来,就是这节讨论的重点问题。在空间允许的情况下,我们尽量把孔和孔的间距拉大,比如在实际工程应用中,AC耦合电容的扇出孔与电容PAD中心距等宽、IC里面的孔间距和IC的PIN pitch相同、其他情况下的孔和孔间距也尽量稍宽点,这就是过孔间距的优化方法,由于孔间距优化有其空间局限性且优化效果对阻抗影响不是那么明显。 所以一般工程师们会花时间在过孔反焊盘的优化上在高速串行信号传输中,较大的反焊盘尺寸和较低的介电常数材料(更好的板材)可以减少电容负载,即提高过孔阻抗,从而减少传输延时。

2)AC耦合电容相邻层挖空优化,如图2所示:

图2

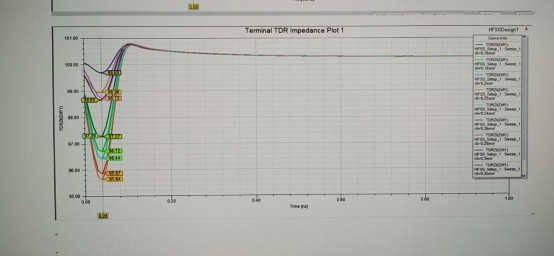

由经验值预估,阻抗和线宽成反比,即线宽越宽,阻抗越小。那么我们的AC耦合电容可以等效成一个比较宽的导线,已知我们常用的C0402电容PAD宽度为20mil,常规100欧姆差分线线宽约为6mil左右。所以在AC耦合电容PAD处阻抗会变小。要增大PAD处的阻抗,可以使PAD和参考面的距离增大。例如我们的AC耦合电容放置在TOP面,那么为了加大PAD处的阻抗,我们选择挖空AC耦合电容下面的L2层平面,这样电容PAD就参考了L3层的地平面,此处的阻抗就会因参考距离增加而阻抗增大。那么又有人会疑问了,我们这里这个L2挖空大小对阻抗大小有影响吗?有最优挖空值吗?这里的答案是肯定的,L2层挖空大小直接影响AC耦合电容出的阻抗大小,具体值我们需要通过仿真软件去估算,模拟实际电容挖空值的好几种可能性,通过仿真数据找出一个最优值。图3是不同挖空值对阻抗影响的示意图,可做参考。

图3

3)减少过孔残桩,必要时背钻孔处理,如图4所示:

图4

电路板过孔残余的电容可以通过如下简单的近似关系得到。除非经过特别小心的处理,一般过孔处的有效特性阻抗,包括经过不同平面的返回路径,是小于50欧姆的,约为35欧姆。50欧姆传输线的单位长度电容为3.3pF/in,那么过孔桩线的单位长度电容约为5pF/in,即约为5fF/mil。根据这一经验法则可以估算出过孔桩线的容性负载。长度为20mil的过孔桩线,它的电容量为20mil*5fF/mil=100fF。位于较厚电路板上长度为100mil的过孔桩线,它的电容量为100mil*5fF/mil=500fF,也就是0.5pF。可预估这单个过孔所产生的时延累加约为0.5*50*0.5pF=12.5ps。说明这个传输信号的时延比相同导线上没有过孔时增加了12.5ps。

所以综上所述,高速串行信号在实际连接中我们要尽量减少过孔穿孔次数,如果芯片摆放在TOP层,AC耦合电容放TOP层,那么我们最好的高速串行信号走线层在靠近bottom面的倒数第三层,倒数第五层,这种情况下过孔残桩最小(可不背钻)。如果倒数第三层,倒数第五层被其他更重要的信号都占掉的情况下,也可以线走到其他层,这种情况下,就需要背钻。背钻的优点是减少杂讯干扰、提高信号完整性、减少盲埋孔的使用,降低PCB制作难度。背钻的作用是钻掉没有起任何连接作用的通孔段,即我们所谓的残桩,避免造成高速信号传输的反射、散射、延时等。减少导通孔对信号完整性带来的影响。

3.总结

所有涉及产品的设计师们都应该了解信号完整性如何影响整个产品的性能。通过在直觉和工程实践的层次上理解信号完整性的基本原理,参与设计过程的每个设计师就能体会到他们的决定对整个系统性能所产生的影响。随着时钟频率越来越高,发现并解决信号完整性问题成为产品研发的关键。精通信号完整性分析技术,并能采取高效的设计过程以便消除这些问题。只有熟练地掌握并运用新的设计规则、新的技术和新的分析工具,才能实现高性能设计,并缩短研发周期,提高项目设计一版成功率。

参考文献:

[1](美)埃里克.伯格丁(Eric Bogatin)著,李玉山等译.信号完整性与电源完整性分析(第三版)北京:电子工业出版社,2019.4