125青岛展芯微电子科技有限公司 266000 山东青岛 34青岛展诚科技有限公司

摘要:集成电路在我们日常生活中扮演着越来越重要的角色,而电子设备的工作环境是一个非常复杂的系统,在这个系统中,静电和电磁干扰是非常常见的问题。当电子设备被这些问题困扰时,静电放电(ESD)会导致电子设备发生故障甚至损坏。在许多情况下,静电放电对集成电路产生干扰,如信号完整性问题和逻辑电路错误。为了防止这些问题对电路造成严重损害,有必要了解ESD的基本原理并掌握,同时做好防护措施。本文将从静电放电的基本原理和基本防护措施两个方面入手,详细介绍集成电路ESD防护措施。

关键词:集成电路;ESD;防护对策

静电是一种自然现象,产生静电的方式多种多样,例如:接触、摩擦、电气设备间的电感应等;例如人体因身体自身的移动、与其他物质的接触、脱离、摩擦力、感生等因素也会产生静电,静电量可达数千至数万伏特;例如在两个电极间,当电极与电极间存在着电势差异时,电极与电极间就会发生电荷输运,直到电极与电极间的电压达到平衡为止。由于静电放电(ElectroStaticDischarge,ESD)对集成电路的影响越来越严重,为保证集成电路的可靠性和稳定性,必须对其进行ESD防护。

1.ESD的产生

静电放电(ElectroStaticDischarge,ESD)是指由于物体表面静电的存在,而产生的电荷累积现象。当物体表面存在电荷时,由于电场的作用,其附近的电子会受到强大电场的作用而发生位移。这种位移就称为静电场位移。当静电力超过了材料所能承受的最大临界值时,就会在材料内部或表面产生电荷积累而导致材料失效,或者产生对其他设备的干扰。ESD是由静电放电引起的现象,静电放电时由于表面上出现了电荷累积而导致静电场位移。ESD放电时有两种形式:一种是空间电荷,一种是表面电荷,其中空间电荷产生的原因是在两个物体之间存在着很小的空间距离(空气间隔),由于空气中存在着大量的自由电子和负离子,使得空气中的空间电荷数量很大,而这种静电电荷可以通过静电感应和静电放电两种方式来产生,静电感应主要是因为当两个物体之间存在着很小的距离时,由于空间电荷量较大,当有一个物体带负电时,其周围就会形成一个强大地电场,这种电场是一种不均匀介质中产生的电磁场,这种电磁场与空间电场相互作用,从而产生了电流,这种电流有很强的穿透力,可以穿透两个物体之间很小距离(空气间隔)而不受阻挡。此外这种电场能够在两个物体之间产生一个很大的电压(通常高于5kV),当两个物体之间距离越大时,产生静电放电电压就越高,但是当两个物体之间距离太小时,也会产生静电放电电流,这种静电放电电流可能会持续数秒至数十毫秒左右。由于静电放电电流是非常微弱的(通常在10μA以下),所以当产生静电放电电流时常常会被忽略掉,但是静电放电电流却是一个非常大的瞬态能量源。由于它的能量非常低,所以也就不能被忽视掉。

2.ESD对电路的影响

在ESD事故中,器件和电路一般都有损坏的可能性。器件损坏主要有以下几种:ESD放电产生的静电在器件上堆积,导致器件损坏;ESD放电过程中,由于寄生电容的作用,将导致电路信号发生畸变;

由于ESD放电的能量是一定的,ESD放电瞬间,将产生很大的热量,导致电路损坏;以上几种情况都会导致电路损坏。因此在设计中对器件和电路进行ESD防护是非常有必要的。

3.集成电路ESD防护对策

集成电路由于具有较高的工作电压、较大的工作电流、较低的工作频率以及较低的可靠性要求等特点,因此在集成电路设计中要将这些特点综合考虑。可以通过以下几种方式对集成电路进行ESD防护。

3.1器件选型

器件选型是对ESD防护最重要的一步,如果选型不合理,将导致ESD防护失效。选择ESD器件的一般原则是:选用有较大耐压的器件,能够承受更大的能量;选用高Q值的器件,即Q值越高,ESD保护能力越强;选用多层材料封装的器件,其厚度要薄,其耐压值要大;选用具有一定耐压值的器件,可以防止ESD放电对电路造成破坏。比如TVS管可以用于抑制浪涌电压和尖峰脉冲电压等。ESD保护器件种类很多,如MOSFET等。在选择ESD保护器件时,可以根据电路工作电压、所需保护能力以及成本等因素进行选择。

3.2设计ESD保护器件

防止 ESD的措施通常是在产品送到顾客手中时才采用,这对最终使用者来说明显是不适宜的。所以,在设计电子产品时,就必须要加入静电放电保护装置,这种保护装置可以是在晶片的外部加入ESD保护装置,或者是在晶片的内部加入ESD保护装置。

3.2.1ESD防护电路

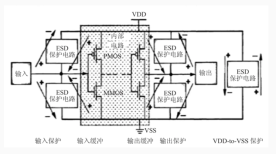

为保护ESD需要增加ESD保护电路,且在 IC正常的工作状态下,ESD保护电路不工作。所以在添加 ESD保护线路时,既要保证 ESD放电回路的高效、迅速,又不能破坏防静电结构本身。在电路正常运行时,抗静电元件不工作,其负面效应(如输入时延)要尽量控制在允许的限度之内,并且要避免 ESD元件出现闩锁现象。芯片内部ESD防护电路如图5所示。

图5芯片内部ESD防护电路图

3.2.2芯片内部ESD防护

ESD保护技术的核心是在芯片上集成静电放电保护单元。芯片内 ESD防护指的是在芯片中集成 ESD防护单元,在静电信号到达时,对内部电路进行保护,使其不被破坏。与芯片外 ESD防护电路相比,其可以明显地提高 ESD防护能力,节约板级空间,降低系统成本,并降低设计与布线的复杂性。由于人体放电模型中的 ESD都是从外部输入的,因此 ESD保护电路一般都与 PAD的引线相邻。在 PAD的输出端,其大容量的 PMOS和 NMOS器件自身可以作为静电保护器件使用。输入 PAD,因为 CMOS电路的输入 PAD通常都是连接到 MOS元件的栅极(gate),栅极氧化层很容易被 ESD所击穿,所以在输入极的旁边,会设置一组 ESD防护电路,以保护输入级的元件。由于 VDD插头和 VSS插头间也会受到 ESD的影响,所以在 VDD插头和 VSS插头旁还需要安装 ESD保护电路。在设计静电保护回路时,应综合考虑不同的 ESD试验方案。ESD防护网络如图4所示。

图4全芯片ESD防护网络

3.3接地

接地是防止ESD的最根本和最有效的办法,接地可以为静电冲击提供一个很好的泄放通道,可以让带电体上积累的静电荷可以顺畅地泄出,并快速地引入到地面中,从而避免了对敏感元件的放电,接地电阻应<10Ω。将作业场所内的人员和设备通过不同的地线进行接地,作业场所内的作业台面应有良好的接地。对于导电的、有静电的物质,例如橡胶等,可采用静电接地。

3.4防静电腕带

直接接触集成元件的人员都应该佩戴防静电腕带,防静电腕带应该与人体皮肤有较好的接触,防静电腕带能够释放出人体上的静电。

3.5湿度控制

空气中的水分对静电电荷的积聚有很大的影响。随着环境湿度的增大,非导体材料表面的电导率也会随之增大,从而使得静电在被测对象表面不容易积累。在有静电的地方,如果工艺条件允许,可以设置空调装置,增加空气中的相对湿度,以消除静电。为了获得最好的静电控效果,应将空气中的相对湿度控制在60%—70%等容许范围内。

3.6静电中和

静电中和指的是通过外部因素对空气进行电离,并通过不同电荷相吸引的原理,使异号电荷与静电源上的电荷向湖中和,同时将同号电荷导向大地,从而将静电源上积累的静电清除掉。离子中和型绝缘体容易产生静电,传统的接地方式不能有效地消除绝缘体的静电,常用的办法是利用离子中和型,也就是在工作环境下,利用离子鼓风机、离子空气枪等。

4结语

ESD是一个看起来微不足道,但实际上却是一个很大的问题。从当前的状况来看,采用片上集成ESD保护电路是比较困难的;随着工艺水平的提高, IC栅氧化物厚度不断变薄, IC本身的抗静电性能不断下降,而在新的工艺水平下,传统的抗静电措施也在不断地被削弱。在芯片中,如何设计一种能够有效抵抗静电干扰的保护装置,是改善集成电路本身抗静电性能的一种有效途径。

参考文献

[1]晁瑞辰.集成电路ESD防护关键技术分析[J].现代工业经济和信息化,2023,13(4):248-250.

[2]罗昱文,张静雅.集成电路ESD防护关键技术探讨[J].设备管理与维修,2019(22):140-141.

[3]马金定.静电释放ESD技术在集成电路防护中的应用[J].集成电路应用,2019,36(7):100-101.